スパッタリング装置

# Adastra

さまざまな分野で培った成膜技術を集約

- 成膜技術の融合・柔軟な装置構成

さまざまな分野で培った成膜技術を集約しユーザーのニーズに合わせ、プロセスマジュールを自由に選択可能

シングルコア ⇄ ダブルコアの変更含め、各フェーズに合わせて柔軟に装置構成の選択・変更が可能

- 省スペース

従来機と比較し、フットプリントを42%削減 (3.3m x 4.2m @ シングルコア)

- 環境への配慮

従来機と比較し、市水使用量を55%削減、エネルギー由來のCO<sub>2</sub>排出量を24%削減

- ユーザビリティ

メンテナンスの作業性向上、リアルタイムモニタリングによる予知保全

スパッタリング装置

# Adastra

## PVD モジュール ラインナップ (AX シリーズ)

### ■ CAELA-AXモジュール Coming Soon

アプリケーション

・メモリ配線

・DRAM セルプレート

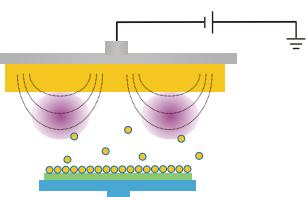

- 平行平板型マグネットロンDCスパッタ

- 独自のカソードマグネットコントロールを採用した CAELAカソードによる高い生産性

- 基板バイアスによる膜質コントロール

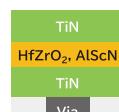

### ■ PDC-AXモジュール Coming Soon

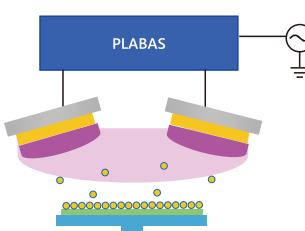

PDC : PLABAS Dual Cathode

PLABAS : Plasma Balanced System

アプリケーション

・誘電体成膜

AlScN, AlN, etc.

・接合の下地膜

・Cu配線用シード,

バリアメタル

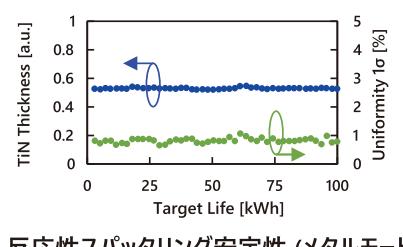

- 当社独自のプラズマ制御技術による

誘電体成膜時におけるターゲットライフ内の

優れたプロセス安定性

- 誘電体膜の高い配向性

- 優れた成膜表面平坦性

### ■ PCM-AXモジュール Coming Soon

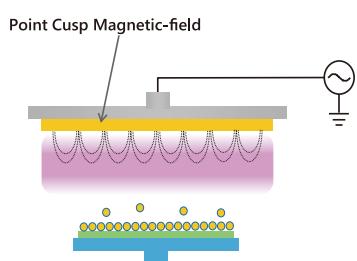

PCM : Point Cusp Magnetic-field

アプリケーション

・メモリ配線

・Cu配線用シード,

バリアメタル

- ポイントカスプ磁場による高イオン化スパッタ

- 低抵抗薄膜成膜

- 高ボトムカバレッジ

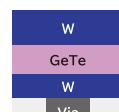

### ■ 4PVD-AXモジュール

アプリケーション

・メモリ素子成膜

・磁気センサ素子

・HDDヘッド

・CMOSイメージセンサ

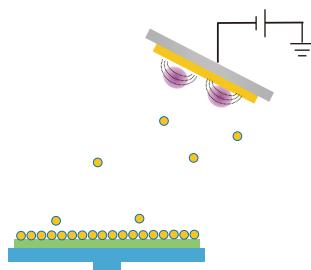

- 最大4カソード搭載可能な、斜め回転スパッタ

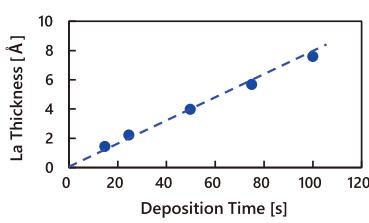

- 原子層レベルの面内均一性と膜厚制御性

- コスパッタリングによる精密な組成比コントロール

- 反応性スパッタの優れた安定性

スパッタリング装置

## 先端半導体を支える薄膜形成装置

# スパッタリング装置 Adastra AX07

### 原子層レベルの面内均一性と膜厚制御性

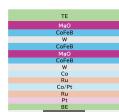

- マルチカソードモジュールを搭載し、超高真空中における多層成膜（最大32カソード）

- 原子層レベルの面内均一性と膜厚制御性

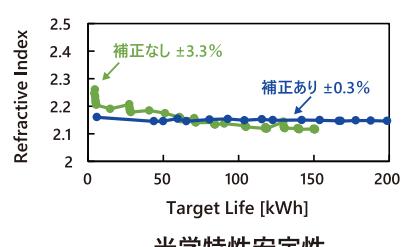

- リアルタイムモニタリング補正※による高いプロセス安定性

※これは、国立研究開発法人新エネルギー・産業総合開発機構(NEDO)の委託業務の成果を活用しています。

#### アプリケーション

MRAM, ReRAMなど各種素子形成

磁気センサ素子, HDDヘッド

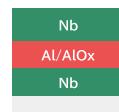

MRAM

MTJ

ReRAM

OTS

based selector

FeRAM

MIM

capacitora

Josephson Junction

(Quantum Computing)

メタル, 酸・窒化膜を原子層レベルで制御未来の多彩なデバイスの製造工程に応用

# スパッタリング装置 IC7500

### 最先端DRAMの量産標準機

- 量産実績に基く高い生産性と安定性

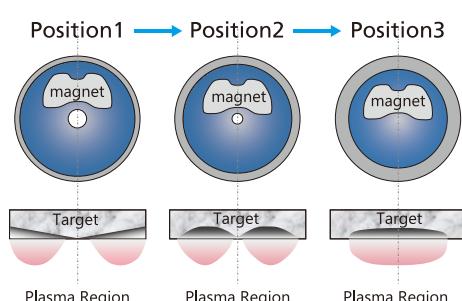

- マグネット位置をIn-situで変更できる独自カソードにより異なる成膜条件やクリーニング条件の連続処理が可能

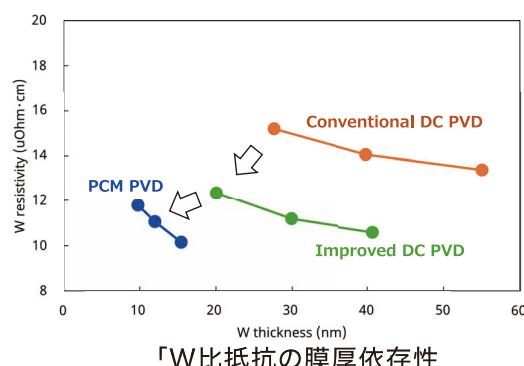

- 低抵抗薄膜成膜(PCM※ PVD)

※PCM:Point Cusp Magnetic-field

#### アプリケーション

メモリ配線, DRAM セルプレート

Cu配線用シード, バリアメタル

DCカソードマグネットコントロール

## 先端半導体を支える薄膜形成装置

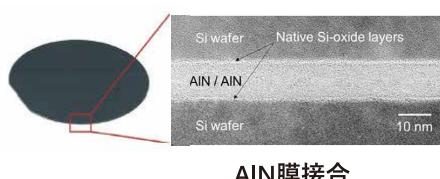

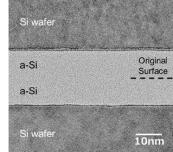

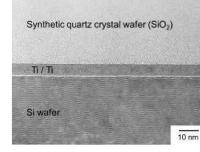

# ウエハー接合装置 BC7300/BC7000 シリーズ

スパッタ膜を利用した接合技術(原子拡散接合法: Atomic Diffusion Bonding)

- スパッタリング膜種による界面抵抗をコントロール

- 無加熱/無加圧での強固な接合

- スパッタリング成膜～接合までを真空一貫処理することによる清浄な接合界面

### アプリケーション

CFET, BSPDN等のウエハー貼り合わせ工程

機能ウエハー製造

AlN膜接合

Si膜接合

Ti膜接合

Courtesy of Frontier Research Institute for interdisciplinary, Tohoku University, Shimatsu Labo.

# スパッタリング装置 FC7100

HKMG(ゲートファースト方式)のデファクトスタンダード

- 原子層レベルの面内均一性と膜厚制御性

- メタルモード/ポイズンモードの両放電領域における安定した反応性スパッタ

- リアルタイムモニタリング補正※による反応性スパッタ時の優れた光学特性安定性

### アプリケーション

High-k メタルゲート

CMOSイメージセンサ

※これは、国立研究開発法人新エネルギー・産業総合開発機構(NEDO)の委託業務の成果を活用しています。